Faire avec les ressources réduites de l'Attiny 2313 n'est pas une affaire simple, il faut réussir à caser un OS et un interpréteur dans 2Ko de flash, un programme dans 128 octets d'EPROM et travailler avec 128 octets de RAM (pour les variables Basic, l'OS ...).

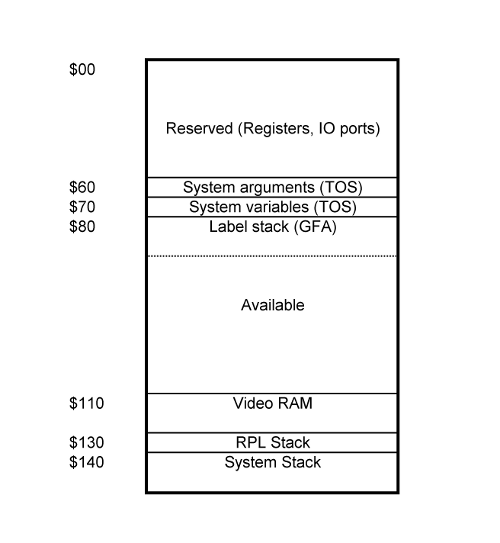

J'ai un temps pensé à utiliser une EEPROM I2C, mais au final je pars sur une première évolution positive en utilisant un Attiny 4313 (que j'ai fini par recevoir après quelques péripéties). Ce dernier a le mérite de doubler les valeur sus-mentionnées, ce qui est déjà beaucoup plus confortable, tout en restant bien sûr 100% compatible avec le 2313. La cartographie mémoire en est simplifiée, et je peux maintenant la dévoiler sans rougir.

Programming an Os and a Basic interpreter with the humble Attiny 2313 is not a simple matter, you have to do with as few as 2Kb of FlashROM, 128 bytes of EPROM (to store the GFA Program) and 128 bytes of RAM.

Therefore, I fist envisaged to use a I2C EEPROM, but dealing with signals synchronization bores me, so I came into a much simpler solution : use a more powerful Attiny 4313. The latter offers twice the room that the 2313 has for every kind of memory. It's now easier to organize memory, and the code is also cleaner. See the memory map hereunder for the details.

lundi 10 décembre 2012

jeudi 25 octobre 2012

It's the final countdown ...

Ce n'est pas tout à fait le compte à rebours de la chanson du groupe Europe, mais c'est une petite application chronomètre, et la première application tout court.

Le chrono ne compte que jusqu'à 4min 15s. La raison est simple, l'interpreteur ne gère pour le moment que les variables 8 bits.

C'est tout de même un grand pas avec la gestion des fonctionnalités suivantes : affectations sur 8 bits, expressions simples (calcul arithmétiques sur des variables et constantes), boucle GOTO, instructions PAUSE, PRINT (avec gestion du ';'), et CLS.

Suivent une photo en action et le code source chargé dans l'EPROM.

Au passage, ce simple programme occupe déjà la quasi totalité des 128 octets de l'EPROM, il va donc falloir que je me penche sur la question d'une EPROM I2C pour stocker le programme GFA.

It's not final, and it's not counting down but up, but it's already quite an achievement for me and the first actual application.

This chrono application counts to 4min 15 s only, due to the fact that the interpreter only handles 8 bits variables.

The following instructions are now supported : 8bits variables, simple arithmetic expressions, loops (GOTO), PAUSE, PRINT (with/without crlf) and CLS.

Hereunder a picture and the source code of the program loaded in the AVR's EPROM. (the later is already almost completely filled with this simple program so an urgent action will be to think about a bigger, I2C interfaced, EEPROM).

Code source :

a|=0

VOID INP(2)

debut:

PAUSE 50

INC a|

m|=a|/60

s|=a| MOD 60

CLS

PRINT m|;":";s|

GOTO debut

Le chrono ne compte que jusqu'à 4min 15s. La raison est simple, l'interpreteur ne gère pour le moment que les variables 8 bits.

C'est tout de même un grand pas avec la gestion des fonctionnalités suivantes : affectations sur 8 bits, expressions simples (calcul arithmétiques sur des variables et constantes), boucle GOTO, instructions PAUSE, PRINT (avec gestion du ';'), et CLS.

Suivent une photo en action et le code source chargé dans l'EPROM.

Au passage, ce simple programme occupe déjà la quasi totalité des 128 octets de l'EPROM, il va donc falloir que je me penche sur la question d'une EPROM I2C pour stocker le programme GFA.

It's not final, and it's not counting down but up, but it's already quite an achievement for me and the first actual application.

This chrono application counts to 4min 15 s only, due to the fact that the interpreter only handles 8 bits variables.

The following instructions are now supported : 8bits variables, simple arithmetic expressions, loops (GOTO), PAUSE, PRINT (with/without crlf) and CLS.

Hereunder a picture and the source code of the program loaded in the AVR's EPROM. (the later is already almost completely filled with this simple program so an urgent action will be to think about a bigger, I2C interfaced, EEPROM).

Code source :

a|=0

VOID INP(2)

debut:

PAUSE 50

INC a|

m|=a|/60

s|=a| MOD 60

CLS

PRINT m|;":";s|

GOTO debut

mercredi 3 octobre 2012

Premier programme GFA AVR

Voici le premier programme GFA exécuté sur OrdiGFA Nano.

Le programme exécuté :

PRINT " Premier programme"

PRINT "GFA BASIC AVR"

Le résultat :

Le programme exécuté :

PRINT " Premier programme"

PRINT "GFA BASIC AVR"

Le résultat :

jeudi 27 septembre 2012

Les outils de développement (suite)

L'OrdiGFA Nano utilise un afficheur LCD commandé par RS485 de la société Droids : le Muin LCD.

Pour pouvoir tester l'envoi correct des données vers l'afficheur LCD, j'ai développé un simulateur de cet afficheur écrit en GFA Basic, à l'aide de l'excellent IDE GBE (hi LP060 !) sous le non moins excellent aranym.

Le programme est exécuté sous l'émulateur Hatari, qui permet d'émuler le port série via un fichier.

En configurant Hatari pour utiliser donc comme port série le fichier généré par le Simulateur/assembleur AVR décrit dans le précédent billet, on peut simuler une partie supplémentaire du Nano.

Pour pouvoir tester l'envoi correct des données vers l'afficheur LCD, j'ai développé un simulateur de cet afficheur écrit en GFA Basic, à l'aide de l'excellent IDE GBE (hi LP060 !) sous le non moins excellent aranym.

Le programme est exécuté sous l'émulateur Hatari, qui permet d'émuler le port série via un fichier.

En configurant Hatari pour utiliser donc comme port série le fichier généré par le Simulateur/assembleur AVR décrit dans le précédent billet, on peut simuler une partie supplémentaire du Nano.

mercredi 26 septembre 2012

Les outils de développement

Pour faciliter le prototypage, j'ai conçu un simulateur/assembleur pour Atmega Attiny, reprenant plus particulièrement les caracteristiques de la carte de développement utilisée, l'AVR-P20 d'Olimex.

Ce simulateur/assembleur est écrit en Java/Swing, et permet l'assemblage du code assembleur en un fichier .hex directement uploadable dans le microcontroleur, et d'un simulateur permettant de concevoir la partie logicielle sur un micro-ordinateur supportant Java.

La plupart du jeu d'instructions AVR est supportée, et l'assembleur génère un fichier "rapport" listant les instructions qu'il gère.

La plupart du jeu d'instructions AVR est supportée, et l'assembleur génère un fichier "rapport" listant les instructions qu'il gère.

La syntaxe gérée par l'assembleur est pour le moment assez contraigante, et les instructions de macro-assemblage sont pour l'heure très limitées.

L'écran ci-contre est assez vide, car les fenêtres de débogage sont celles de l'éditeur Eclipse. Je prévois dans une prochaine version d'afficher des informations pertinentes (registres, mémoire, eeprom, série) dans des fenêtres dédiées. La sortie série est néanmoins facile à débugguer car disponible dans un fichier de type "serial.out".

Ce simulateur/assembleur est écrit en Java/Swing, et permet l'assemblage du code assembleur en un fichier .hex directement uploadable dans le microcontroleur, et d'un simulateur permettant de concevoir la partie logicielle sur un micro-ordinateur supportant Java.

La syntaxe gérée par l'assembleur est pour le moment assez contraigante, et les instructions de macro-assemblage sont pour l'heure très limitées.

L'écran ci-contre est assez vide, car les fenêtres de débogage sont celles de l'éditeur Eclipse. Je prévois dans une prochaine version d'afficher des informations pertinentes (registres, mémoire, eeprom, série) dans des fenêtres dédiées. La sortie série est néanmoins facile à débugguer car disponible dans un fichier de type "serial.out".

OrdiGFA Nano, premier prototype

Ce projet commence par la réalisation d'une première plateforme prototype : l'OrdiGFA Nano.

L’originalité logicielle de cette nouvelle machine est de

faire du GFA Basic le langage principal d’exploitation du matériel.

Il s’agit donc de s’affranchir des nombreuses couches

logicielles présentes sur les ordinateurs du marché, et d’avoir le Basic comme

langage de prédilection dans l’esprit des ordinateurs 8 bits des années 1980.

Cependant, là où à l’époque le Basic en question était très

souvent le Microsoft Basic, l’idée est ici d’utiliser le GFA Basic, plus puissant

et plus riche.

A l’avenir, si un système d’exploitation s’avère utile, il

faudrait envisager la réalisation « sur mesure » d’un DOS-like écrit

en GFA/AVR.

De même, l’objectif de ce projet étant de retrouver un

maximum l’expérience de la programmation en GFA Basic sur ST, il y a réimplémentation des appels systèmes du

système d’exploitation Atari TOS, et notamment de certaines fonctions BIOS, BDOS

et XBIOS (la partie CP/M 68k donc).

But du projet

Le projet OrdiGFA a débuté le 3 septembre dernier, et a été abordé en suivant l'état de l'art de la gestion de projet informatique, avec charte et plan projet, dossier d'architecture et spécifications détaillées.

En attendant de mettre en ligne les documents correspondants, voici la description tout droit extraite de la charte projet :

En attendant de mettre en ligne les documents correspondants, voici la description tout droit extraite de la charte projet :

Le but de ce projet, nom de code « Ordi GFA», est la conception d’un ordinateur compatible au niveau source

avec le Basic GFA du micro-ordinateur Atari ST, offrant également une certaine

compatibilité au niveau API avec le système d’exploitation de l’Atari ST, le

TOS.

Ce projet a pour but d’offrir une plateforme

moderne aux fans de programmation en GFA Basic, et s’adresse donc

principalement à ces derniers.

L’objectif n’est pas de concevoir une

machine « mainstream » mais plutôt d’ouvrir les portes à d’autres

initiatives du même genre. Par ailleurs, la possibilité de faire fonctionner

des applications graphiques fluides (jeux ou démos) n’est pas un objectif, ceci

en raison de l’approche amatrice et des contraintes techniques (compétences,

matériel, temps, ressources).

Le budget n’est pas fixe est dépend

exclusivement de la bonne volonté des participants, il en va de même pour le

planning qui sera fonction de la disponibilité de chaque intervenant (approche

hobbyiste).

mardi 25 septembre 2012

Nouveau projet

Ce blog se consacre à la description du projet OrdiGFA et à son évolution au fil du temps. Le projet est déjà bien démarré dans sa version "nano", et les premiers billets se succéderont rapidement pour décrire les différentes étapes déjà achevées ou bien débutées.

Inscription à :

Articles (Atom)